# 温度制御型プログラマブル MOSFET ドライバ

# ISL25700

ISL25700 は、8 ビット D/A コンバータ 2 系統とオーバーカレント保護機能をモノリシック CMOS IC 上に集積した、高機能な温度制御型 MOSFET ドライバです。

対象点の温度をモニターし、ユーザーが設定したセットポイントと比較して、設定温度に到達するまで出力を駆動します。ISL25700のほかに、外付けのパワーMOSFET、ヒーター、およびNTCサーミスタを使って温度制御ループを構成します。

電流の上限値を設定できる MOSFET のオーバーカレント保護機能も備えており、出力電圧を自動的に調整してMOSFET パワーをユーザー定義リミット以下に維持します。保護設定は電流リミット違反を引き起こす可能性のある温度設定よりも優先します。

アプリケーションが自由に使える 8 ビット汎用 D/A コンバータを 2 系統搭載しています。

ISL25700 は一定温度の維持が必要なアプリケーションに最適です。

# アプリケーション\*(17ページ参照)

- マイクロ恒温槽を用いた次のような温度制御アプリケーション

- 基地局

- 分光器

- プレシジョンメーター

- プレシジョンジェネレータ

# 特長

- I<sup>2</sup>C シリアルインタフェースを介してセットポイント の設定が可能

- セットポイントの温度範囲:+40°C~+110°C

- 動作温度範囲: -40°C ~ +125°C

- セットポイント初期精度:3°C

- セットポイントの粗調整および微調整

- 粗調整範囲 +15°C

- 微調整範囲 +0.1°C

- ・ 長期ドリフト誤差:±0.5℃

- 外付け MOSFET のプログラマブルな電流保護

- 5ビットのゲイン設定

- 電源電圧範囲: 3V ~ 15V

- 20kΩ から 200kΩ の外付け NTC サーミスタに対応

- 汎用 8 ビット D/A コンバータ、出力分解能 0.4%

- 高い信頼性

- 耐久性:各レジスタのビットあたり1万回のデータ 書き換え

- レジスタデータ保持: T ≦ +125°C にて 10 年間

- 10 リード μTFDN 2.1mm×1.6mm パッケージ

- 鉛フリー(RoHS 準拠)

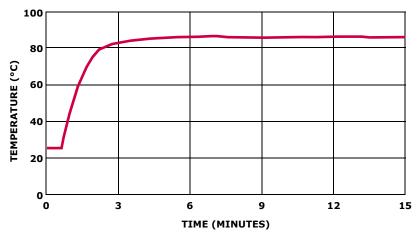

図 1. 温度セトリング時間の代表的特性

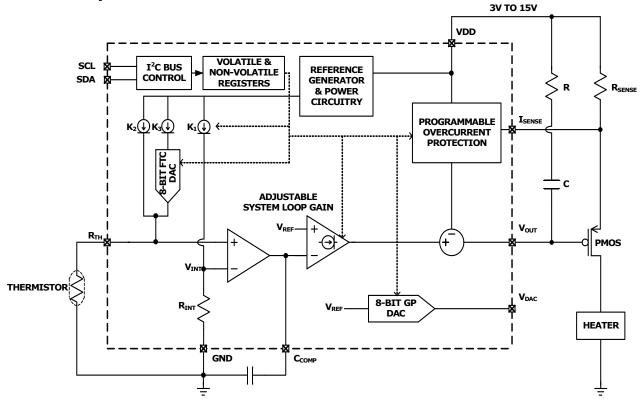

# ブロック図 / アプリケーション回路

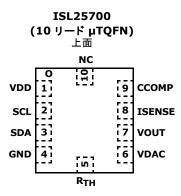

# ピン配置

# ピンの説明

| μTQFN<br>ピン番号 | ピン名称            | 説明                                                                                                                                                                                                                                                               |

|---------------|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1             | VDD             | 電源。デバイスの動作に必要な電源を与えます。                                                                                                                                                                                                                                           |

| 2             | SCL             | $I^2C$ インタフェースの入力クロック。 $I^2C$ シリアルインタフェースのシリアルクロック入力です。SCL には外付けプルアップ抵抗が必要です。ピンが開放のときに入力が中間電位とならないように、およそ $3M\Omega$ のプルダウン抵抗が内蔵されています。                                                                                                                          |

| 3             | SDA             | $I^2C$ インタフェースのオープンドレインシリアル入出力。SDA は $I^2C$ インタフェースの双方向シリアルデータ入出力です。 $I^2C$ マスターデバイスが出力するデバイスアドレス、オペコード、およびデータを、シリアルクロック SCL の立ち上がりエッジで取り込みます。また、シリアルクロックの立ち下がりエッジでデータを出力します。 SDA ピンには外付けプルアップ抵抗が必要です。ピンが開放のときに入力が中間電位とならないように、およそ $3M\Omega$ のプルダウン抵抗が内蔵されています。 |

| 4             | GND             | グランド。デバイスのバイアスグランドおよび基準グランドです。                                                                                                                                                                                                                                   |

| 5             | R <sub>TH</sub> | 外付け NTC サーミスタ。外付け NTC サーミスタはホイートストンブリッジの一辺を構成し、RTH ピンと GND の間に接続します。                                                                                                                                                                                             |

| 6             | VDAC            | DAC 出力。高精度な $8$ ビット $D/A$ コンバータの出力です。 $D/A$ コンバータの出力電圧範囲はデフォルトで $0V$ から $2V$ です。 $D/A$ コンバータの出力電圧範囲を $2$ 倍にするには、ゲインコントロールレジスタの $DAC$ ゲインビット $Reg.03h[6]$ を $1$ にセットします。                                                                                          |

| 7             | VOUT            | 外付け P チャネル MOSFET の制御出力。ホイートストンブリッジの不平衡に比例して外付け P-MOSFET を駆動します。                                                                                                                                                                                                 |

| 8             | ISENSE          | 電流センス入力。外付け電流センス抵抗 RSENSE 両端の電圧低下をモニターします。電流センスレジスタ Reg. $01h[7:3]$ 設定した電圧低下リミット値を ISENSE が超えると、P-MOSFET の電力損失が制限されます。                                                                                                                                           |

| 9             | ССОМР           | 補償コンデンサ。デバイスの安定性を高めるために、補償用のセラミックコンデンサを CCOMP ピンと グランド間に接続します。容量値は 30pF から 1000pF です。このコンデンサを介してオペアンプに負帰還が与えられます。                                                                                                                                                |

| 10            | NC              | 内部回路には接続されていません。                                                                                                                                                                                                                                                 |

# 注文情報

| 部品番号<br>(備考 1, 2, 3) | マーキング | リールあたりの<br>個数 | 温度範囲(℃)     | パッケージ<br>(鉛フリー)     | パッケージの<br>外形図 |

|----------------------|-------|---------------|-------------|---------------------|---------------|

| ISL25700FRUZ-T       | GT    | 3000          | -40 to +125 | 10 Ld 2.1x1.6 μTQFN | L10.2.1x1.6A  |

| ISL25700FRUZ-TK      | GT    | 1000          | -40 to +125 | 10 Ld 2.1x1.6 μTQFN | L10.2.1x1.6A  |

| ISL25700FRUZ-T7A     | GT    | 250           | -40 to +125 | 10 Ld 2.1x1.6 μTQFN | L10.2.1x1.6A  |

## 備考:

- 1. リールの詳細仕様については Technical Brief「Tape and Reel Specification for Integrated Circuit (TB347)」を参照してください。

- 2. これら鉛フリーのプラスチックパッケージ製品には、専用の鉛フリー素材、モールド素材、ダイアタッチ素材を採用するとともに、RoHS 指令に準拠し、かつ、Pb はんだ付け作業および鉛フリーはんだ付け作業と互換性のある e4 端子外装処理の NiPdAu メッキを施しています。インターシルの鉛フリー製品は鉛フリーピークリフロー温度において MSL 分類に対応し、この仕様は IPC/JEDEC J STD-020 の鉛フリー要件と同等か上回るものです。

- 3. 湿度感受性レベル (MSL) については <u>ISL25700</u> のデバイス情報ページを参照してください。MSL の詳細については Technical Brief「<u>Guidelines for Handling and Processing Moisture Sensitive Surface Mount Devices (TB363)</u>」を参照してください。

FN6885.0 2010年9月3日

## 絶対最大定格

| すべてのデジタルインタフェースピン電圧、              |

|-----------------------------------|

| GND 基準0.3V ~ +6V                  |

| $V_{DD}$ 0.3V $\sim$ +16.5V       |

| ESD 定格                            |

| 人体モデル(JESD22-A114F にて試験)5kV       |

| 機械モデル(JESD22-A115Bにて試験)200V       |

| ラッチアップ +125℃ にて Class II. Level A |

## 温度情報

| 熱抵抗(代表値)                       | $\theta_{ m JA}$ | (°C/W) | θ <sub>JC</sub> (°C/W)                |

|--------------------------------|------------------|--------|---------------------------------------|

| 10 リード μTQFN パッケージ             | (備考 4, 5)        | 135    | 75                                    |

| 保存温度範囲                         |                  | –65    | $^{\circ}$ C $\sim$ +150 $^{\circ}$ C |

| 最大接合部温度(プラスチッ                  | クパッケージ           | ジ)     | +150°C                                |

| 鉛フリー・リフロープロファ                  |                  |        | URL を参照                               |

| http://www.intersil.com/pbfree | /Pb-FreeRefl     | ow.asp |                                       |

#### 推奨動作条件

| 温度範囲(インダストリアル)  | 40°C ∼ +125°C             |

|-----------------|---------------------------|

| V <sub>DD</sub> | $\dots \dots 3V \sim 15V$ |

注意:過度に長い期間にわたって最大定格点または最大定格付近でモジュールを動作させないでください。そのような動作条件を課すと製品の信頼性に影響が及ぶ恐れがあるとともに、保証の対象とはならない可能性があります。

#### 備考:

- 4. θ<sub>JA</sub> はデバイスを放熱効率の高い試験基板に実装し自由大気中で測定した値です。詳しくは Technical Brief「<u>Thermal Characterization of Packaged Semiconductor Devices (TB379)</u>」を参照してください。

- 5.  $\theta_{JC}$ の測定における「ケース温度」位置はパッケージ上面の中心です。

#### アナログ特性 特記のない限り推奨動作条件の範囲に適用。太字のリミット値は動作温度範囲である −40°C から +125°C に対して適用されます。

| 記号                                  | パラメータ                                          | 試験条件                                                                      |           | MIN<br>(備考 13) | TYP<br>(備考 6)         | MAX<br>(備考 13)  | 単位            |

|-------------------------------------|------------------------------------------------|---------------------------------------------------------------------------|-----------|----------------|-----------------------|-----------------|---------------|

| T <sub>SET</sub>                    | Temperature Set Point                          | T <sub>SET</sub> must be above MIN                                        |           |                | 40                    |                 | °C            |

|                                     |                                                | ambient                                                                   | MAX       |                | 110                   |                 | °C            |

|                                     | Temperature Set Point Accuracy                 | 3 sigma standard deviati                                                  | on        |                | ±3                    |                 | °C            |

| T <sub>SET_COARSE</sub>             | Coarse Adjustment of Set Point                 | R <sub>TH</sub> = 100k @ +25°C,<br>B <sub>25/85</sub> = 4100k ( 備考 14     | 1)        |                | 15                    |                 | °C            |

| T <sub>SET_FINE</sub>               | Fine Adjustment of Set Point                   |                                                                           |           |                | 0.1                   |                 | °C            |

| T <sub>SET_FINE_INL</sub><br>(備考 9) | Fine Control Integral<br>Non-linearity         |                                                                           |           | -2.5           | ±0.9                  | +2.5            | LSB<br>(備考 7) |

| T <sub>SET_FINE_DNL</sub><br>(備考 8) | Fine Control Differential<br>Non-linearity     |                                                                           |           | -2             | ±0.5                  | +2              | LSB<br>(備考 7) |

| T <sub>DRIFT</sub>                  | Long-term Drift of Set Point                   | 1000h, Reg.1 = x2h, Reg<br>Reg.3 = 90h                                    | .2 = 80h, |                | ±0.5                  |                 | °C            |

| I <sub>TH</sub>                     | Thermistor Current Range                       |                                                                           |           | 25             | 40                    | 55              | μΑ            |

| R <sub>TH</sub>                     | NTC Thermistor Range                           | Resistance @ +25°C                                                        |           | 20             | 100                   | 200             | kΩ            |

| V <sub>OUT</sub>                    | External P-MOSFET Gate Voltage                 | I <sub>OUT</sub> = 0μA                                                    |           | 0.25           |                       | V <sub>DD</sub> | V             |

|                                     | V <sub>OUT</sub> Swing @ Fixed V <sub>DD</sub> | I <sub>OUT</sub> = 0μA                                                    | MIN       |                | V <sub>DD</sub> - 2.5 |                 | V             |

| I <sub>OUT</sub>                    | Output Current                                 |                                                                           |           |                |                       | 7               | μΑ            |

| V <sub>SENSE</sub>                  | Overcurrent Protection Set Point               | V <sub>SENSE</sub> = I <sub>SENSE</sub> x R <sub>SEN</sub><br>see Table 3 | SE;       |                | 200 to 1750           |                 | mV            |

| GENERAL PU                          | RPOSE DAC (MEASUREMENTS                        | S BETWEEN GND AND V                                                       | DAC)      |                |                       | 11              |               |

| V <sub>DAC MAX</sub>                | Maximum DAC Output                             | Using internal $V_{REF}$ , $V_{DD}$ load, Gain = 1                        | ≤ 5V, No  |                | 2                     | 2.5             | V             |

|                                     |                                                | V <sub>DD</sub> > 5V, No load, Gain = 2                                   |           |                | 4                     | 5.0             | V             |

| INL<br>(備考 9)                       | Integral Non-Linearity                         | No load                                                                   |           | -1             | ±0.4                  | +1              | LSB<br>(備考 7) |

| DNL<br>( 備考 8)                      | Differential Non-linearity                     | No load                                                                   |           | -0.75          | ±0.3                  | +0.75           | LSB<br>(備考 7) |

| V <sub>DAC_OFFSET</sub>             | Offset                                         | DAC register set to 0, No load                                            |           | 0              | 0.2                   | 1               | LSB<br>(備考 7) |

| R <sub>OUT</sub>                    | DAC Output Impedance                           |                                                                           |           |                | 350                   |                 | Ω             |

# **アナログ特性** 特記のない限り推奨動作条件の範囲に適用。**太字のリミット値は動作温度範囲である −40°C から +125°C に対して適用されます。(続き)**

| 記号                             | パラメータ                        | 試験条件                                             | MIN<br>(備考 13) | TYP<br>(備考 6) | MAX<br>(備考 13) | 単位     |

|--------------------------------|------------------------------|--------------------------------------------------|----------------|---------------|----------------|--------|

| PSRR                           | Power Supply Rejection Ratio | DAC at middle scale, frequency from 0Hz to 25kHz |                | -85           |                | dB     |

| TC <sub>V</sub><br>(備考 10, 11) | Temperature Coefficient      | DAC register set between 20 hex and FF hex       |                | ±45           |                | ppm/°C |

# **動作特性** 特記のない限り推奨動作条件の範囲に適用。**太字のリミット値は動作温度範囲である -40°C から** +125°C に対して**適用**されます。

|                             |                                                                        |                                                                                                                              | MIN                   | TYP    | MAX     |        |

|-----------------------------|------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------|-----------------------|--------|---------|--------|

| 記号                          | パラメータ                                                                  | 試験条件                                                                                                                         | (備考 13)               | (備考 6) | (備考 13) | 単位     |

| I <sub>DD1</sub>            | V <sub>DD</sub> Supply Current<br>(Non-Volatile Write/read)            | $f_{SCL} = 400 kHz$ ; SDA = Open;<br>(for $I^2C$ , Active, Read and Write<br>States) $I_{PMOS} = 0 mA$ , DAC unload          |                       |        | 4       | mA     |

| I <sub>DD2</sub>            | V <sub>DD</sub> Supply Current<br>(Volatile Write/read)                | I <sub>PMOS</sub> = 0mA, DAC unload                                                                                          |                       |        | 2.8     | mA     |

| I <sub>LkgDig</sub>         | Leakage Current, at SDA and SCL Pins                                   | Voltage at pin from GND to VCC                                                                                               | -2                    |        | 2       | μΑ     |

| t <sub>DAC</sub><br>(備考 11) | DAC Settling Time                                                      | From bus STOP condition to V <sub>DAC</sub> change                                                                           |                       |        | 3       | μs     |

| V <sub>POR</sub>            | Power-On Recall Voltage                                                | Minimum V <sub>DD</sub> at which memory recall occurs                                                                        |                       | 2.5    | 2.9     | V      |

| V <sub>DD</sub> Ramp        | V <sub>DD</sub> Ramp Rate                                              | @ any level from 0V to 15V                                                                                                   | 0.2                   |        | 50      | V/ms   |

| t <sub>D</sub><br>(備考 11)   | Power-Up Delay                                                         | V <sub>DD</sub> above V <sub>POR</sub> , to DAC Register recall completed, and I <sup>2</sup> C Interface in standby state   |                       |        | 1       | ms     |

| EEPROM S                    | PECIFICATIONS                                                          |                                                                                                                              |                       |        |         |        |

|                             | EEPROM Endurance                                                       |                                                                                                                              | 10,000                |        |         | Cycles |

|                             | EEPROM Retention                                                       | Temperature ≤ +55°C                                                                                                          | 50                    |        |         | Years  |

|                             |                                                                        | Temperature ≤ +125°C                                                                                                         | 10                    |        |         | Years  |

| SERIAL IN                   | ITERFACE SPECIFICATIONS                                                |                                                                                                                              |                       |        |         |        |

| $V_{I2C}$                   | I <sup>2</sup> C Bus Voltage                                           | $V_{I2C} \leq V_{DD}$                                                                                                        | 2.7                   |        | 5.5     | V      |

| $V_{ m IL}$                 | SDA, and SCL Input Buffer<br>LOW Voltage                               | V <sub>I2C</sub> from 2.7V to 5.5V                                                                                           |                       |        | 0.8     | V      |

| V <sub>IH</sub>             | SDA, and SCL Input Buffer<br>HIGH Voltage                              | V <sub>I2C</sub> from 2.7V to 5.5V                                                                                           | 1.4                   |        |         | V      |

| Hysteresis<br>(備考 11)       | SDA and SCL Input Buffer<br>Hysteresis                                 |                                                                                                                              | 0.05*V <sub>I2C</sub> |        |         | V      |

| V <sub>OL</sub><br>(備考 11)  | SDA Output Buffer LOW<br>Voltage, Sinking 4mA                          |                                                                                                                              | 0                     |        | 0.4     | V      |

| Cpin<br>(備考 11)             | SDA, and SCL Pin Capacitance                                           |                                                                                                                              |                       |        | 10      | pF     |

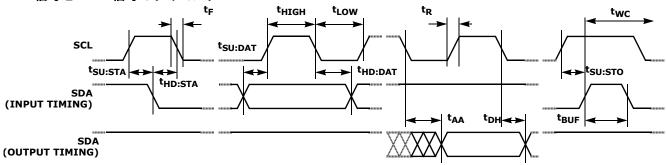

| f <sub>SCL</sub>            | SCL Frequency                                                          |                                                                                                                              |                       |        | 400     | kHz    |

| t <sub>IN</sub><br>(備考 11)  | Pulse Width Suppression Time at SDA and SCL Inputs                     | Any pulse narrower than the max spec is suppressed                                                                           |                       |        | 50      | ns     |

| t <sub>AA</sub><br>(備考 11)  | SCL Falling Edge to SDA<br>Output Data Valid                           | SCL falling edge crossing 30% of V $_{\rm I2C}$ , until SDA exits the 30% to 70% of V $_{\rm I2C}$ window                    |                       |        | 900     | ns     |

| t <sub>BUF</sub><br>(備考 11) | Time the Bus Must be Free<br>Before the Start of a New<br>Transmission | SDA crossing 70% of $V_{I2C}$ during a STOP condition, to SDA crossing 70% of $V_{I2C}$ during the following START condition | 1300                  |        |         | ns     |

| t <sub>LOW</sub>            | Clock LOW Time                                                         | Measured at the 30% of $V_{I2C}$ crossing                                                                                    | 1300                  |        |         | ns     |

| t <sub>HIGH</sub>           | Clock HIGH Time                                                        | Measured at the 70% of $V_{I2C}$ crossing                                                                                    | 600                   |        |         | ns     |

## 動作特性

特記のない限り推奨動作条件の範囲に適用。太字のリミット値は動作温度範囲である -40°C から+125°C に対して適用されます。(続き)

| 記号                                | パラメータ                                        | 試験条件                                                                                                                                          | MIN<br>(備考 13)   | TYP<br>(備考 6) | MAX<br>(備考 13) | 単位 |

|-----------------------------------|----------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|------------------|---------------|----------------|----|

| <sup>t</sup> SU:STA               | START Condition Setup Time                   | SCL rising edge to SDA falling edge. Both crossing 70% of $V_{\rm I2C}$ .                                                                     | 600              |               |                | ns |

| <sup>t</sup> HD:STA               | START Condition Hold Time                    | From SDA falling edge crossing 30% of $V_{I2C}$ to SCL falling edge crossing 70% of $V_{I2C}$                                                 | 600              |               |                | ns |

| t <sub>SU:DAT</sub>               | Input Data Setup Time                        | From SDA exiting the 30% to 70% of $V_{12C}$ window, to SCL rising edge crossing 30% of $V_{12C}$                                             | 100              |               |                | ns |

| t <sub>HD:DAT</sub>               | Input Data Hold Time                         | From SCL falling edge crossing 70% of $V_{I2C}$ to SDA entering the 30% to 70% of $V_{I2C}$ window                                            | 0                |               |                | ns |

| t <sub>SU:STO</sub>               | STOP Condition Setup Time                    | From SCL rising edge crossing 70% of $V_{I2C}$ , to SDA rising edge crossing 30% of $V_{I2C}$                                                 | 600              |               |                | ns |

| t <sub>DH</sub>                   | Output Data Hold Time                        | From SCL falling edge crossing 30% of $V_{I2C}$ , until SDA enters the 30% to 70% of $V_{I2C}$ window                                         | 0                |               |                | ns |

| t <sub>R</sub>                    | SDA and SCL Rise Time                        | From 30% to 70% of V <sub>I2C</sub>                                                                                                           | 20 +<br>0.1 * Cb |               | 250            | ns |

| t <sub>F</sub>                    | SDA and SCL Fall Time                        | From 70% to 30% of V <sub>I2C</sub>                                                                                                           | 20 +<br>0.1 * Cb |               | 250            | ns |

| Cb                                | Capacitive Loading of SDA or SCL             | Total on-chip and off-chip                                                                                                                    | 10               |               | 400            | pF |

| Rpu<br>(備考 11)                    | SDA and SCL Bus Pull-Up<br>Resistor Off-Chip | Maximum is determined by $t_R$ and $t_F$ .<br>For Cb = 400pF, max is about $2\sim2.5k\Omega$<br>For Cb = 40pF, max is about $15\sim20k\Omega$ | 1                |               |                | kΩ |

| t <sub>WC</sub><br>(備考<br>11, 12) | Non-Volatile Write Cycle Time                |                                                                                                                                               |                  | 15            | 20             | ms |

#### 備考:

- 6. TYP 値は、T<sub>A</sub> = +25°C、電源電圧 +12V での値です。

- 7. LSB: [VDAC $_{255}$  VDAC $_{0}$ ]/255。ここで VDAC $_{255}$  と VDAC $_{0}$  は、汎用 DAC レジスタ Reg.04h[7:0] をそれぞれ FFh および 00h に設定したときの DAC の出力電圧です。

- 8. DNL = [VDAC<sub>i</sub> VDAC<sub>i-1</sub>]/LSB-1, for i = 1 to 255。ここで i は汎用 DAC レジスタ Reg.04h[7:0] の設定値。

- 9. INL =  $[VDAC_i (i \cdot LSB + VDAC_0)]/LSB$  for i = 1 to 255

$${\sf TC_V} = rac{{\sf VDAC_i(T) - VDAC_i(40^{\circ}C)}}{{\sf VDAC_i(40^{\circ}C)}} imes rac{{10^6}}{{(T - 40)^{\circ}C}} \ , \ {\sf for} \ i = 1 \ {\sf to} \ 255, \ \ T = -40^{\circ}C \ \sim +125^{\circ}C, \ 40^{\circ}C \ {\it E}$$

基準。

- 11. リミット値は特性評価にて得ており、製品では試験していません。

- 12.  $t_{WC}$  は、 $I^2C$  シリアルインタフェースのライト動作でのライトシーケンスの終了における有効な STOP 条件から、内部不揮発性レジスタへのライトサイクルまでの時間です。不揮発性レジスタへのライトサイクルの終了は BUSY 状態のポーリングで確認できます。

- 13. MIN リミットおよび MAX リミットを有するパラメータは、特記のない限り、+25°C にて全数試験を行っています。温度リミットは特性評価にて得ており、製品では試験していません。

- 14.  $B_{25/85}$  はサーミスタ素材固有の定数で、抵抗値と温度の関係を表したグラフの傾きを表します。

# SCL 信号と SDA 信号のタイミング

# 代表的な性能特性

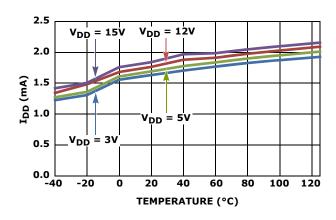

図 2. 電源電流 I<sub>DD</sub> vs V<sub>DD</sub>

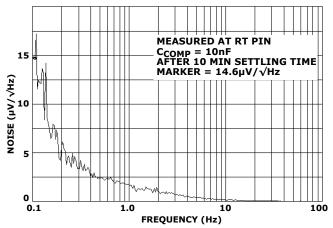

図 3. 閉ループアプリケーションでの  $R_{TH}$  入力における ノイズレベル、 $2\mu V/\sqrt{Hz}$  @ 1Hz

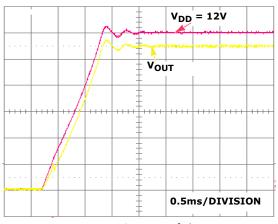

図4. VOUTパワーアップディレイ

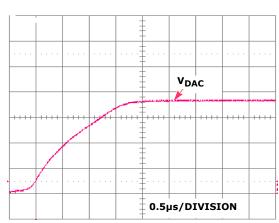

図 5. 汎用 DAC のセトリング時間 (フルスケール、ゲイン = 2)

# 代表的な性能特性(続き)

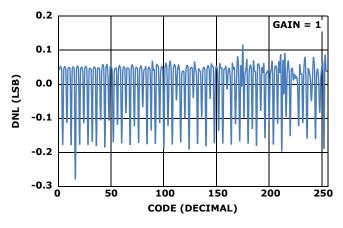

図 6. 汎用 DAC  $\sigma$  DNL vs DAC コード値、 $V_{DD}=3V$

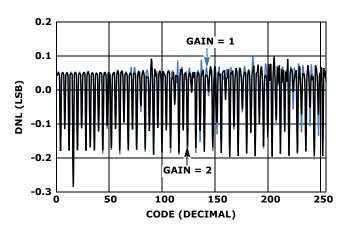

図 7. 汎用 DAC の DNL vs DAC コード値、 $V_{DD}=5V$

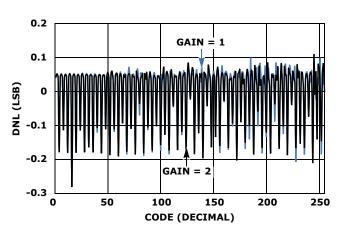

図 8. 汎用 DAC の DNL vs DAC コード値、 $V_{DD}=15V$

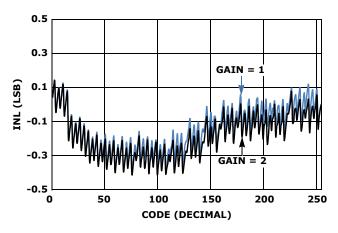

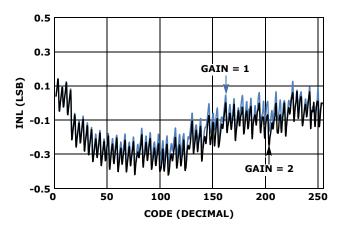

図 9. 汎用 DAC の INL vs DAC コード値、V<sub>DD</sub> = 3V

図 10. 汎用 DAC の INL vs DAC コード値、 $V_{DD}=5V$

図 11. 汎用 DAC の INL vs DAC コード値、 $V_{DD}=15V$

# 代表的な性能特性(続き)

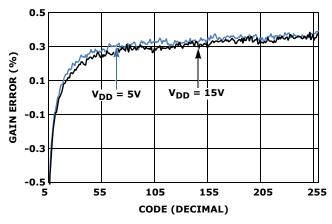

図 12. 汎用 DAC のゲイン誤差

# 動作の仕組み

ISL25700 は外部物体の温度および外部 P-MOSFET の損失を高精度に制御する MOSFET ドライバです。NTC サーミスタの抵抗値を連続的にセンスし、P-MOSFET (温度制御要素)の電流を調整して温度を制御します。

ISL25700 は、物体の温度と  $I^2$ C シリアルインタフェースを介してユーザーが設定した目標温度セットポイント ( $T_{SET}$ ) とを比較し、その差に逆比例する形で P-MOSFET を駆動します。外付け NTC サーミスタを使ってセンスした外部温度をホイートストンブリッジとアンプを用いて駆動電圧に変換します。電流モードのホイートストンブリッジの一辺は外付け NTC サーミスタとプログラマブル8ビット FTC DAC で構成され、他の一辺は内部抵抗  $R_{INT}$ に電流を供給するプログラマブル電流ソース K1 で構成されています。

8 ビット FTC DAC は  $+15^{\circ}$ C の粗調整温度ウインドウ内に設定した  $T_{SET}$  を  $+0.1^{\circ}$ C 以下の精度で微調整する役割を担います。 $T_{SET}$  温度は、粗調整温度制御レジスタ Reg.01h [2:0] と、微調整温度制御レジスタ Reg.02h[7:0] で設定します。詳しくは 10 ページの「レジスタマップ」セクションを参照してください。サーミスタの抵抗値、R/T カーブタイプ、誤差、NTC 傾きなどのパラメータと、ホイートストンブリッジの辺を流れる電流比の調整によって、 $T_{SET}$  が  $+15^{\circ}$ C の温度粗調整ウィンドウの範囲に収まるように設定します。なお  $T_{SET}$  は具体的なアプリケーションで見込まれる最高周囲温度よりも高くなければなりません。

システムゲインは、ゲインコントロールレジスタ Reg.03h [4:0] を使って、ステップあたり 0.35dB で 32 ステップの 範囲で設定します。総システムゲインを調整することで、外付け部品を使用することなくサーマルシステムの発振を防止できます。

P-MOSFET の電力損失の制御と設定には電流センスレジスタ Reg.01h[7:3] を使用します。この設定機能によって、初期ターンオン時のヒート曲線の調整と、P-MOSFET のオーバーヒートが回避できます。電流をセンスするにはP-MOSFETと直列に接続する外付け抵抗 $R_{\rm SENSE}$ が必要です。 $R_{\rm SENSE}$ 値によって電流リミット値が決まります。実効的な電圧降下が 200mV から 1750mV の範囲で、かつ、MOSFET が安全動作領域(SOA)になるように、 $R_{\rm SENSE}$ を選択してください。

汎用 8 ビット DAC である GP DAC の出力電圧  $V_{DAC}$  は汎用 DAC レジスタ Reg.04h[7:0] で設定します。汎用 DAC の出力振幅はゲインコントロールレジスタの DAC ゲインビット Reg.03h[6] で設定します。ゲインコントロールレジスタの DAC イネーブルビット Reg.03h[7] を 0 にすると、汎用 DAC はディスエーブル状態になります。

#### レジスタマップ

デバイスには揮発性 (RAM) と不揮発性 (EEPROM) の2 種類のレジスタバンクが搭載されています。アドレス 00hから 07hの揮発性レジスタのレジスタ名称およびビット定義と、不揮発性レジスタのレジスタ名称およびビット定義とは同一です。パワーアップ時にすべてのデータは不揮発性レジスタから呼び出される揮発性レジスタに保持されます。パワーアップ後に揮発性レジスタと不揮発性レジスタに独立してライト/リードするには、コントロール/ステータスレジスタの NV ビット Reg.08h[7]を1に設定します。ただし、不揮発性レジスタへのライトは対応する揮発性レジスタからのリードはできません。すべてのデータは対応する揮発性レジスタからリードされます。

デバイスのレジスタマップを表1に示します。

表 1. ISL25700 のレジスタマップ

|                                                   | レジスタ | ピット定義         |             |        |        |        |        |        |        |        |

|---------------------------------------------------|------|---------------|-------------|--------|--------|--------|--------|--------|--------|--------|

| レジスタ名                                             | アドレス | 7             | 6           | 5      | 4      | 3      | 2      | 1      | 0      | デフォルト値 |

| デバイス ID(リードオンリー)                                  | 00h  | ID[7]         | ID[6]       | ID[5]  | ID[4]  | ID[3]  | ID[2]  | ID[1]  | ID[0]  | 00h    |

| 電流センス /<br>粗調整温度制御                                | 01h  | CS[4]         | CS[3]       | CS[2]  | CS[1]  | CS[0]  | CTC[2] | CTC[1] | CTC[0] | 03h    |

| 微調整温度制御                                           | 02h  | FTC[7]        | FTC[6]      | FTC[5] | FTC[4] | FTC[3] | FTC[2] | FTC[1] | FTC[0] | 80h    |

| ゲインコントロール<br>(DAC イネーブル /DAC ゲイン /<br>システムループゲイン) | 03h  | DAC<br>Enable | DAC<br>Gain | NA     | SLG[4] | SLG[3] | SLG[2] | SLG[1] | SLG[0] | 90h    |

| 汎用 DAC                                            | 04h  | DAC[7]        | DAC[6]      | DAC[5] | DAC[4] | DAC[3] | DAC[2] | DAC[1] | DAC[0] | 80h    |

| 汎用レジスタ 1                                          | 05h  | GP1[7]        | GP1[6]      | GP1[5] | GP1[4] | GP1[3] | GP1[2] | GP1[1] | GP1[0] | 00h    |

| 汎用レジスタ 2                                          | 06h  | GP2[7]        | GP2[6]      | GP2[5] | GP2[4] | GP2[3] | GP2[2] | GP2[1] | GP2[0] | 00h    |

| R <sub>INT</sub> 絶対誤差(リードオンリー)                    | 07h  | sign bit      | ERR[6]      | ERR[5] | ERR[4] | ERR[3] | ERR[2] | ERR[1] | ERR[0] | XX     |

| コントロール / ステータスレジスタ<br>(不揮発性のみ)                    | 08h  | NV            | NA          | NA     | NA     | NA     | NA     | NA     | BUSY   | 00h    |

## デバイス ID レジスタ(Reg.00h[7:0])

リードオンリーレジスタです。デバイス ID コード 00h が 格納されています。

#### 粗調整温度制御 (Reg.01h[2:0])

3ビットの設定によって温度セットポイントの7種類の粗調整ウィンドウのひとつを選択します。デフォルトのセットポイントは、 $R_{TH}$ が  $100k\Omega$ で +25°C での温度係数が -4.25%°C のサーミスタを接続した場合に、およそ+59°C に相当します。温度セットポイントは +40°C から+110°C の動作温度範囲であればいずれの値にも変更できるほか、異なる抵抗値または R/T カーブタイプ(NTC 傾き)特性のサーミスタも使えます。その場合、式 1 の $R_{INT}/R_{TH}$  の比に従って、セットポイントが +15°C の粗調整範囲ウィンドウに収まるように、粗調整ウィンドウを設定します。

$$\frac{R_{INT}(T)}{R_{TH}(setpoint)} = \frac{K2 + K3 \times \frac{Code}{255}}{K1} \tag{$\vec{\mathfrak{T}}$ 1)}$$

ここで、

$R_{INT}$ :ホイートストンブリッジの一辺を構成する内蔵 $9k\Omega$ 抵抗。

K1、K2、K3:ホイートストンブリッジの各辺の電流の比を表す係数。

Code: 微調整温度制御レジスタ Reg.02h[7:0] に設定した 10 進数での値。

内蔵抵抗  $R_{\rm INT}$  の抵抗値は ISL25700 のデバイスごとに異なるほか、パッケージ温度にも依存します。温度 T における実際の  $R_{\rm INT}$  は式 2 で求めます。

$$R_{\text{INT}}(T) = R_{\text{INT}}(25)x[1 + \alpha(T - 25) + \beta(T - 25)^2] \tag{$\pm 2$}$$

ここで、

$R_{\text{INT}}(25) = 9000 + R_{\text{INT}}$  絶対誤差 ×15 : +25 $^{\circ}$ C における内蔵抵抗値で、単位は  $\Omega$ 。

$R_{\rm INT}$  絶対誤差:  $R_{\rm INT}$  絶対誤差 Reg.07h[7:0] に格納されている絶対誤差を 10 進に変換した符号付き整数。ビット 7 は符号を表し、0 が「+」、1 が「-」。

$\alpha = -1337 \times 10^{-6}$  : 一次温度係数、ppm/°C

$β = 5 \times 10^{-6}$  : 二次温度係数、ppm/°C<sup>2</sup>

T: 摂氏を単位とする温度。

粗調整温度制御レジスタ Reg.01h[2:0]のそれぞれの設定に対応した K1、K2、K3 の各係数とサーミスタの抵抗範囲を表 2 に示します。

表 2. 粗調整温度範囲

| レジスタ<br>01h[2:0] | K1 | К2      | КЗ | セットポイントにおける<br>サーミスタ<br>抵抗範囲(kΩ) |  |  |

|------------------|----|---------|----|----------------------------------|--|--|

| 000              |    | 使用できません |    |                                  |  |  |

| 001              | 3  | 3       | 2  | 5.4 ~ 9.0                        |  |  |

| 010              | 4  | 3       | 2  | 7.2 ~ 12.0                       |  |  |

| 100              | 5  | 3       | 2  | 9.0 ~ 15.0                       |  |  |

| 011              | 7  | 3       | 2  | 12.6 ~ 21.0                      |  |  |

| 101              | 8  | 3       | 2  | 14.4 ~ 24.0                      |  |  |

| 110              | 9  | 3       | 2  | 16.2 ~ 27.0                      |  |  |

| 111              | 12 | 3       | 2  | 21.6 ~ 36.0                      |  |  |

#### 電流センススレッショルド(Reg.01h[7:3])

電流リミットのトリップポイントを設定するレジスタです。設定した電圧スレッショルドを  $I_{SENSE}$  ピンの印加電圧が下回ると  $V_{OUT}$  は High になり、その結果、 $I_{SENSE} \times R_{SENSE}$  に比例する負帰還ループが形成されます。レジスタの値は表 3 に基づいて設定します。

表 3. 電流センススレッショルド

|          | センス抵抗の                                                      | 誤差の TYP 値(%)  |                       |  |  |

|----------|-------------------------------------------------------------|---------------|-----------------------|--|--|

| レジスタ     | 電圧低下<br>スレッショルド                                             |               |                       |  |  |

| 01h[7:3] | V <sub>DD</sub> - (I <sub>SENSE</sub> ×R <sub>SENSE</sub> ) | $V_{DD} = 3V$ | V <sub>DD</sub> = 15V |  |  |

| 00000    | V <sub>DD</sub> - 200mV                                     | ±5            | +20                   |  |  |

| 00001    | V <sub>DD</sub> - 250mV                                     | ±5            | +20                   |  |  |

| 00010    | V <sub>DD</sub> - 300mV                                     | ±5            | +20                   |  |  |

| 00011    | V <sub>DD</sub> - 350mV                                     | ±5            | +20                   |  |  |

| 00100    | V <sub>DD</sub> - 400mV                                     | ±5            | +20                   |  |  |

| 00101    | V <sub>DD</sub> - 450mV                                     | ±5            | +20                   |  |  |

| 00110    | V <sub>DD</sub> - 500mV                                     | ±5            | +20                   |  |  |

| 00111    | V <sub>DD</sub> - 550mV                                     | ±5            | +20                   |  |  |

| 01000    | V <sub>DD</sub> - 600mV                                     | ±5            | +20                   |  |  |

| 01001    | V <sub>DD</sub> - 650mV                                     | ±5            | +20                   |  |  |

| 01010    | V <sub>DD</sub> - 700mV                                     | ±5            | +20                   |  |  |

| 01011    | V <sub>DD</sub> - 750mV                                     | ±5            | +20                   |  |  |

| 01100    | V <sub>DD</sub> - 800mV                                     | ±5            | +20                   |  |  |

| 01101    | V <sub>DD</sub> - 850mV                                     | ±5            | +20                   |  |  |

| 01110    | V <sub>DD</sub> - 900mV                                     | ±5            | +20                   |  |  |

| 01111    | V <sub>DD</sub> - 950mV                                     | ±5            | +20                   |  |  |

| 10000    | V <sub>DD</sub> - 1000mV                                    | ±5            | +20                   |  |  |

| 10001    | V <sub>DD</sub> - 1050mV                                    | ±5            | +20                   |  |  |

| 10010    | V <sub>DD</sub> - 1100mV                                    | ±5            | +20                   |  |  |

| 10011    | V <sub>DD</sub> - 1150mV                                    | ±5            | +20                   |  |  |

| 10100    | V <sub>DD</sub> - 1200mV                                    | ±5            | +20                   |  |  |

| 10101    | V <sub>DD</sub> - 1250mV                                    | ±5            | +20                   |  |  |

| 10110    | V <sub>DD</sub> - 1300mV                                    | ±5            | +20                   |  |  |

| 10111    | V <sub>DD</sub> - 1350mV                                    | ±5            | +20                   |  |  |

| 11000    | V <sub>DD</sub> - 1400mV                                    | ±5            | +20                   |  |  |

| 11001    | V <sub>DD</sub> - 1450mV                                    | ±5            | +20                   |  |  |

| 11010    | V <sub>DD</sub> - 1500mV                                    | ±5            | +20                   |  |  |

| 11011    | V <sub>DD</sub> - 1550mV                                    | ±5            | +20                   |  |  |

| 11100    | V <sub>DD</sub> - 1600mV                                    | ±5            | +20                   |  |  |

| 11101    | V <sub>DD</sub> - 1650mV                                    | ±5            | +20                   |  |  |

| 11110    | V <sub>DD</sub> - 1700mV                                    | ±5            | +20                   |  |  |

| 11111    | V <sub>DD</sub> - 1750mV                                    | ±5            | +20                   |  |  |

# 微調整温度制御レジスタ(Reg.02h[7:0])

あらかじめ設定した粗調整温度制御レジスタ Reg.01h[2:0] の範囲内で、8 ビット FTC DAC に適切なコードを設定して最終温度  $T_{SET}$  を微調整するレジスタです。最終温度  $T_{SET}$  はステップあたりおよそ  $+0.07^{\circ}$ C の増減で微調整可能です。

# システムループゲイン(Reg.03h[4:0])

総システムループゲインを表 4 記載のとおりステップあたり ±0.35dB で 5 ビットの範囲で設定します。

デフォルトのシステムループゲインは、MOSFET タイプ、熱伝導率、および周囲温度からの遮断度合いで異なります。

表 4. システムループゲインの設定

| Reg.03h[4:0] | ループゲインの設定 (dB) |  |  |  |  |

|--------------|----------------|--|--|--|--|

| 00000        | -5.60          |  |  |  |  |

| 00001        | -5.25          |  |  |  |  |

| 00010        | -4.90          |  |  |  |  |

| 00011        | -4.55          |  |  |  |  |

| 00100        | -4.20          |  |  |  |  |

| 00101        | -3.85          |  |  |  |  |

| 00110        | -3.50          |  |  |  |  |

| 00111        | -3.15          |  |  |  |  |

| 01000        | -2.80          |  |  |  |  |

| 01001        | -2.45          |  |  |  |  |

| 01010        | -2.10          |  |  |  |  |

| 01011        | -1.75          |  |  |  |  |

| 01100        | -1.40          |  |  |  |  |

| 01101        | -1.05          |  |  |  |  |

| 01110        | -0.70          |  |  |  |  |

| 01111        | -0.35          |  |  |  |  |

| 10000        | 初期ゲイン(デフォルト)   |  |  |  |  |

| 10001        | 0.35           |  |  |  |  |

| 10010        | 0.70           |  |  |  |  |

| 10011        | 1.05           |  |  |  |  |

| 10100        | 1.40           |  |  |  |  |

| 10101        | 1.75           |  |  |  |  |

| 10110        | 2.10           |  |  |  |  |

| 10111        | 2.45           |  |  |  |  |

| 11000        | 2.80           |  |  |  |  |

| 11001        | 3.15           |  |  |  |  |

| 11010        | 3.50           |  |  |  |  |

| 11011        | 3.85           |  |  |  |  |

| 11100        | 4.20           |  |  |  |  |

| 11101        | 4.55           |  |  |  |  |

| 11110        | 4.90           |  |  |  |  |

| 11111        | 5.25           |  |  |  |  |

# DAC イネーブルおよび DAC ゲイン (Reg.03h[7:6])

DAC イネーブルビット Reg.03h[7] を 0 にすると、汎用 DAC レジスタ Reg.04h[7:0] の設定にかかわらず、DAC 出力はディスエーブルになります。DAC イネーブルビット Reg.03h[7] を 1 にすると、DAC 出力は DAC ゲインビット Reg.03 [6] および汎用 DAC レジスタ Reg.04h[7:0] の設定内容で決まります。

DAC ゲインビット Reg.03h[6] が 0 のとき DAC の出力電圧 範囲は 0V から 2V です。すなわちゲイン = 1 です。DAC ゲインビット Reg.03h[6] が 1 のとき、ゲインは 2 となって、DAC 出力電圧範囲は 0V から 4V になります。

## 汎用 DAC レジスタ(Reg.04h[7:0])

GP DAC の入力に値を直接書き込んで出力電圧を設定する 8 ビットのレジスタです。レジスタのデフォルト値は80h です。DAC の出力電圧範囲は DAC ゲインビットReg.03h[6] の設定によって異なります。

# 汎用レジスタ 1 および汎用レジスタ 2(Reg.05h および Reg.06h)

アプリケーションに開放されている 8 ビットの汎用不揮発性レジスタおよび揮発性レジスタです。較正データの格納やシステム情報の格納に使えます。

## R<sub>TNT</sub> 絶対誤差レジスタ(Reg.07h[7:0])

内部抵抗  $R_{\rm INT}$  の公称値と実際値の差を格納するレジスタです。  $R_{\rm INT}$  の公称値は  $9k\Omega$  で、抵抗両端の電圧低下が温度セットポイントを表します。  $R_{\rm INT}$  の絶対誤差の LSB 重みは  $15\Omega$  です。  $R_{\rm INT}$  の計算は式 2 を参照してください。

## コントロール / ステータスレジスタ (Reg.08h[7:0])

NV ビット Reg.08h[7] は、データのリードおよびライトの対象を不揮発性レジスタか揮発性レジスタに指定するビットです。このビットを 0 にすると、すべての動作は不揮発性レジスタが対象になり、データは同時に揮発性レジスタに複製されます。このビットを 1 にすると、すべての動作は揮発性レジスタのみが対象になります。NVビット Reg.08h[7] のデフォルト値は 0 です。

BUSY ビット Reg.08h[0] はリードオンリーです。1 のとき、不揮発性レジスタへのライトサイクルが進行中であることを示します。このビットを読み出すことで、NACK 方式を用いることなく、ひとつ前のライトの完了を確認してから次のライトサイクルの発行に移ることができます。

# ${f I^2C}$ シリアルインタフェース

ISL25700 は双方向のバスプロトコルを採用しています。このプロトコルでは、バスにデータを送出するデバイスをトランスミッタとして定義し、バスのデータを受信するデバイスをレシーバとして定義します。転送を制御するデバイスはマスターであり、転送を制御されるデバイスはスレーブです。マスターはデータ転送を開始する役割と、送信動作および受信動作のそれぞれでクロックを与える役割を担います。ゆえに ISL25700 は、すべてのアプリケーションにおいてスレーブデバイスとして動作します。

13

$I^2C$  インタフェース上では、すべてのデータバイトは MSB を先頭に送信されます。

#### プロトコルの説明

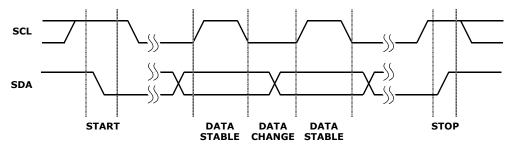

SDA ラインのデータ遷移は SCL が Low 期間にのみ許されています。 SCL が High 期間中の SDA ステート遷移は START 条件と STOP 条件を示すために予約されています(図 13 を参照)。 ISL25700 のパワーアップ後は SDA ピンは入力モードになります。

すべての  $I^2$ C インタフェース動作は、SCL が High 期間中に SDA が High から Low に遷移する START 条件から始まります。ISL25700 は SDA と SCL ラインを連続的に監視して START 条件を検出します。START 条件が満たされない限りいかなるコマンドにも応答しません(図 13参照)。ただし、パワーアップシーケンス中と不揮発性レジスタへの内部ライトサイクル中は、START 条件は無視されます。

すべての I<sup>2</sup>C インタフェース動作は、SCL が High 期間中に SDAに Low から High に遷移する STOP 条件で終結します(図 13 参照)。各リード動作の終了時の STOP 条件、または揮発性レジスタに対するライト動作の終了によって、デバイスはスタンバイモードに移行します。不揮発性レジスタへのライトに対して STOP 条件が発行されると、不揮発性レジスタに対する実際のライトサイクルが始まります。不揮発レジスタへの内部ライトサイクルが完了するとデバイスはスタンバイモードに移行します。

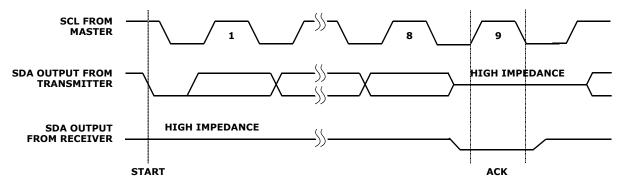

アクノレッジ「ACK」はデータ転送の成功に使われる便宜上の表記です。マスターあるいはスレーブいずれかの送信デバイスは、8 ビット送信後に SDA バスを解放します。レシーバは9番目のクロックサイクル中に SDA ラインを Low に引き込んで8 ビットデータの受信を示します(図 14)。

ISL25700 は、START 条件を認識したあと、有効な識別バイトと正しいアドレスバイトを受信すると ACK で応答します。ISL25700 はライト動作のデータバイトの受信後にも ACK で応答します。リード動作の場合、マスターはデータバイトの受信後に ACK で応答します。

有効な識別バイトの上位7ビットは0101000bで構成されています。LSB はリード / ライトビットです。1 はリード動作を表し、0 はライト動作を表します(表5 参照)。

#### 表 5. 識別パイトの形式

| 0     | 1 | 0 | 1 | 0 | 0 | 0 | R/W   |

|-------|---|---|---|---|---|---|-------|

| (MSB) |   |   |   |   |   |   | (LSB) |

FN6885.0 2010年9月3日

図 13. 有効なデータ変化、スタート条件、ストップ条件

図 14. レシーバからの ACK 応答

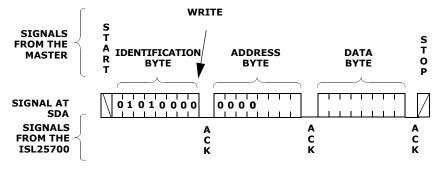

図 15. バイトライトシーケンス

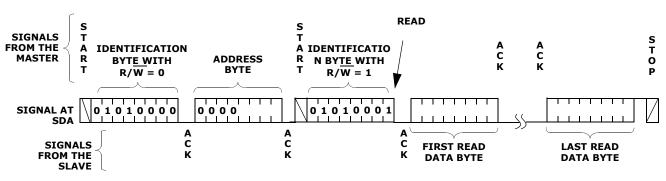

図 16. リードシーケンス

# ライト動作

ライト動作は、START条件に続いて、有効な識別バイト、有効なアドレスバイト、データバイト、およびSTOP条件で構成されます。識別バイト、アドレスバイト、データバイトの3バイトそれぞれに対してISL25700はACKで応答します。このとき、データバイトは揮発性レジスタにのみ書き込まれたあと、デバイスはスタンバイモードに移行します。不揮発性レジスタにもデータバイトを書き込むように設定されている場合は、ISL25700は不揮発性レジスタへの内部ライトサイクルを開始します。不揮発性レジスタへの内部ライトサイクルの間、ISL25700はSDAピンおよびSCLピンの遷移を無視するとともに、SDA出力をハイインピーダンス状態にします。不揮発性レジスタへの内部ライトサイクルが終了すると、ISL25700はスタンバイ状態に移行します(図14参照)。

データバイトを揮発性レジスタのみに書き込むか、または不揮発性レジスタにも書き込むかは、コントロール / ステータスレジスタの NV ビット Reg.08h[7] で指定します(10 ページの「レジスタマップ」を参照)。なお、不揮発性レジスタへの連続書き込みには 20ms の間隔が必要です。

#### ポーリング制御

不揮発性レジスタへのライトサイクルが進行中かどうかはコントロール / ステータスレジスタの BUSY ビット Reg.08h[0] をポーリングすることで分かります (13ページの「コントロール / ステータスレジスタ (Reg.08h[7:0])」を参照)。BUSY ビット Reg.08h[0] が 1 のとき、不揮発性レジスタへの内部ライトサイクルが進行中です。この場合、マスターは次のライトサイクルを発行してはなりません。不揮発性レジスタへの内部ライトサイクルが終了するとBUSY ビット Reg.08h[0] は 0 になります。

# リード動作

リード動作は 3 バイトの命令と 1 バイト以上のデータバイトで構成されます (図 16 を参照)。マスターは、START条件、R/W ビットが 0 の識別バイト、アドレスバイト、2回目の START条件、R/W ビットが 1 の 2 個目の識別バイトというシーケンスを発行してリード動作を開始します。 3 バイトのそれぞれで ISL25700 は ACK で応答します。続いて ISL25700 はデータバイトを出力します。 ISL25700 がデータバイトの最終ビットを出力すると、マスターは STOP条件を発行してリード動作を終結します(図 16 参照)。

データバイトを揮発性レジスタから読み出すか、または不揮発性レジスタから読み出すかは、コントロール / ステータスレジスタの NV ビット Reg.08h[7] で指定します (10ページの「レジスタマップ」を参照)。

# アプリケーション情報

適切な温度制御を行うには、サーミスタを適切に選択するとともに、システム全体を正しく較正することが重要です。サーミスタの選択手順および較正手順を以下に示します。

- 1. サーミスタタイプを選択し、メーカーから RT 特性を 入手します。

- 2. 所望の温度におけるサーミスタ抵抗値を求め、対応する粗調整温度範囲を表 2 から探します。セットポイントにおけるサーミスタの抵抗値は粗調整範囲内になければなりません。なお、粗調整温度範囲は互いに重複しています。

- 3. サーマル発振を防ぐとともに高速なセトリングを得るために、電流センスレジスタ Reg.01h[7:3] とゲインコントロールレジスタのシステムループゲインビット Reg.03h[4:0] にできるだけ大きな値を設定します。

- 4. 外部温度センサーを使用してシステム較正を実行し 微調整行います。

#### サーミスタの選択

所望の温度セットポイント  $T_{SET}$  における抵抗値が、表 2 の範囲に収まるサーミスタを選択します。サーミスタの R/T 特性は、表またはグラフの形式で、通常はメーカーから提供されます。

たとえば、 $T_{SET}$  = +91.5°C で温度を安定させたい場合を考えてみます。サーミスタには Vishay 社の 100k $\Omega$  NTC サーミスタ NTCS0805E3104FXT を使用すると仮定します。 Vishay がウェブ上(http://www.vishay.com/doc?29100)で提供している Microsoft Excelのワークシートを用いて計算すると、このサーミスタの +91.5°C における抵抗値は 8109.12 $\Omega$  と求まります。この値を表 2 に当てはめると、粗 調整温度範囲の設定値は 001b または 010b になることが わかります。

## 電流センス抵抗と MOSFET の選択

電流センス抵抗  $R_{SENSE}$  は、システムの最大消費電力、最大電流、最小分解能などを考慮して選択します。  $R_{SENSE}$  の推奨値は  $0.1\Omega$  から  $10\Omega$  の範囲です。 $0.1\Omega$  の抵抗を使うと最大電流は 2A から 17.5A の範囲に制限され、 $10\Omega$  の抵抗を使うと電流リミットは 20mA から 175mA の範囲に制限されます。適切な電力定格となるように電流センス抵抗のタイプとサイズを選択してください。

ISL25700 は P タイプのパワーMOSFET またはダーリントンペアとの組み合わせでのみ動作します。ドライブ能力が限られているためバイポーラトランジスタは駆動できません。パワー MOSFET はマイクロ恒温槽内でヒーターとして使われます。

## システムループゲインの設定

アプリケーション回路を、ISL25700、パワーMOSFET、発熱要素、およびサーミスタなどを使って構成します。システムループゲインによって帰還系の熱安定性が決まります。言い換えると、あるセットポイントを別のセットポイントに変更したときに、パワー MOSFET を流れる電流を発振を起こすことなく短時間でセトリングさせなければなりません。なお電流のセトリング時間は、電流プローブを使ってオシロスコープで観測します。

ボード線図を解析してシステムの位相マージンを求める 方法でもシステムの安定性がわかります。ゲインおよび 位相マージンのボード線図は、RTHピンからサーミスタ を切り離してループを崩し、 $R_{TH}$  ピンとサーミスタの間に低周波シグナルアナライザを接続して取得します。この方法でシステムの伝達関数と周波数との関係が解析できます。なお、サーミスタは外部電源によって  $30\mu A$  の DC 電流でバイアスされている点に注意してください。シグナルアナライザを使って入力ノード( $R_{TH}$ )で周波数を掃引し、出力ノード(1サーミスタ)の位相変化を測定します。経験則として、システムゲインが 10dB に到達したとき、15°以上の位相マージンが必要です。

システムループゲインは一度決めたらできるだけ変更しないでください。

#### 較正手順

回路をパワーアップし、粗調整温度制御レジスタ Reg.01h[2:0] を 001b にプログラムします。較正済みの外部温度センサーを使ってサーミスタの温度を測定します。サーミスタの温度が安定したら、所望の温度となるように、外部温度センサーが +91.5°C (この例の場合)を指すまで微調整温度制御レジスタ Reg.02h[7:0] の値を変更します。

式1と式2を用いて次のように10進のFTC コードを求めます。

$$Code = \frac{K1 \times R_{INT}(T) - K2 \times R_{TH}(T)}{K3 \times R_{TH}(T)} \times 255$$

(式 3)

なお、最終的なアプリケーションシステム温度は、許容されている消費電力と、周囲温度からの遮断度合いによって異なります。

汎用レジスタ1 Reg.05h[7:0] および汎用レジスタ2 Reg.06h [7:0] には2 点の温度ポイントに対応する較正値を格納することができます。3 点以上の温度ポイントに対する較正値をルックアップテーブルとして保存する場合は外部メモリを使用してください。

#### デバイスの配置とレイアウトの注意事項

精度を維持し、かつ、サーミスタとデバイス間のグランドトレース長をできるだけ短くするために、ISL25700 とサーミスタはできるだけ近くに配置してください。デバイスのグランドピンとシステムのグランドは、 $R_{TH}$  帰還ピンがコモングランドノイズを拾わないように、「一点グランド」として単一点で接続してください。

ISL25700 はサーミスタから離して遮蔽領域の外に配置することもできますが、周囲温度範囲が広くなるため、セットポイント精度は低下します。式 2 に基づくルックアップテーブルを用いてセットポイントのずれを防止してください。

VDD ピンの近くに、デカップリングのために、 $0.1\mu F$  と  $1\mu F$  のコンデンサを並列に配置してください。

パワーアップ時に MOSFET に大電流スパイクが流れないように、P-MOSFET のゲートには  $500k\Omega$  以上のプルアップ抵抗か 2 ページの「ブロック図 / アプリケーション回路」に記載したようなハイパス RC フィルタを接続してください。ハイパスフィルタの時定数は  $1\mu$ s から  $20\mu$ s の範囲に設定してください。

# 改訂履歴

この改訂履歴は参考情報として掲載するものであり、正確を期すように努めてはいますが、内容を保証するものではありません。最新のデータシートについてはインターシルのウェブサイトをアクセスしてください。

| 日付       | レビジョン    | 変更点 |

|----------|----------|-----|

| 2010/9/3 | FN6885.0 | 初版  |

# 製品

インターシルは高性能アナログ半導体の設計および製造に関する世界的なリーダーです。当社の製品は、フラットパネルディスプレイ、携帯電話、ハンドヘルド製品、ノートパソコンなど、急速な成長を遂げているマーケットを対象としています。インターシルではパワーマネージメント機能とアナログ信号処理機能に対応した製品ファミリを取り揃えています。製品ファミリの詳細についてはwww.intersil.com/product\_tree/をアクセスしてください。

\*アプリケーション、関連ドキュメント、関連部品については、www.intersil.com内のISL25700のページを参照してください。

本データシートに関するご意見や誤りのご指摘は www.intersil.com/askourstaff からご連絡ください。

信頼性に関するデータは rel.intersil.com/reports/search.php を参照してください。

インターシルのそのほかの製品については www.intersil.com/product\_tree/ を参照してください。

インターシルは、www.intersil.com/design/quality/に記載の品質保証のとおり、ISO9000 品質システムに基づいて、製品の製造、組み立て、試験を行っています。

インターシルの製品は製品に関する情報のみを提供して販売されます。インターシルは、予告なしにいかなる時点においても、回路設計、ソフトウェア、仕様を変更する権利を有します。したがいましてお客様におかれては、部品を発注する前に、データシートが最新であることをご確認くださるようにお願いいたします。インターシルが提供する情報は正確かつ信頼できうるものと考えておりますが、その使用に関して、インターシルおよび関連子会社は責を負わないものとします。また、その使用に関して、第三者が所有する特許または他の知的所有権の非侵害を保証するものではありません。インターシルおよび関連子会社が所有する特許の使用権を暗黙的または他の方法によって与えるものではありません。

インターシルの会社概要については www.intersil.com をアクセスしてください。

FN6885.0 2010 年 9 月 3 日

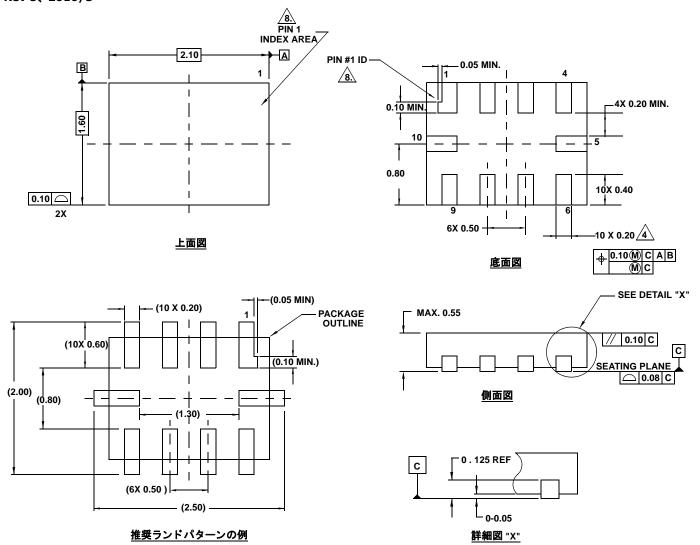

# パッケージ寸法図

#### L10.2.1x1.6A

10 LEAD ULTRA THIN QUAD FLAT NO-LEAD PLASTIC PACKAGE Rev 5、2010/3

#### 備考:

- 1. 寸法と公差は ASME Y14.5m-1994 に従っています。

- 2. 寸法の単位は mm です。角度の単位は度です。 ()内の寸法は参考値です。

- 3. 特記のない限り、公差は DECIMAL ±0.05 です。

- 4. リード幅はメッキ端子に適用され、端子先端から 0.15mm ~ 0.30mm のポイントで計測した値です。

- 5. パッケージの反りの最大は 0.05mm です。

- 6. 許容されるバリの最大寸法は各方向とも 0.076mm です。

- 次の点を除き JEDEC MO-255UABD と同一です。

リードプルバックなし、パッケージ厚さの MIN 値は 0.50mm ではなく 0.45mm リード長さ寸法は 0.42mm ではなく 0.45mm MAX

- 8. 1ピンの識別子はオプションですが、表示されているゾーン内に配置されます。1ピンの識別子はモールドまたはマーキングで示されます。